The Phase-2 upgrades of CMS and ATLAS at the High Luminosity LHC will require a new tracker with readout electronics operating in extremely harsh radiation environment and high data rate readout. In fact, during the Long Shutdown 3, both silicon tracking systems will be entirely replaced because of the accumulated radiation damage and to take advantage of the increased luminosity.

The harsh environment of HL-LHC, including a peak luminosity of 5x1034 cm-1s-1 and an estimated total dose (TID) up to 1.4 Grad through its lifetime is placing strong requirements on the radiation tolerance of the chip.

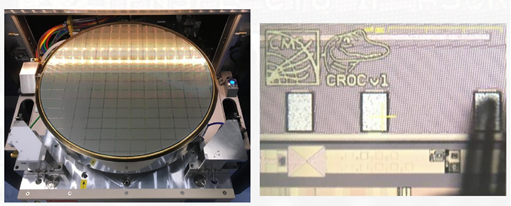

The RD53 collaboration is a joint effort between the two experiments facing the challenges of characterizing the CMOS 65nm technology in radiation environment and developing hybrid pixel readout chips for the upgrades of the pixel detectors of both experiments.

After an intensive radiation campaign which allowed to provide fundamental guidelines to design chips which are tolerant to such high radiation levels, a half- size demonstrator, called RD53A, was produced in 2017 to qualify the chosen 65nm CMOS technology and compare different analog front-ends and digital architectures for the development of the final chips.

This prototype has been also extensively used by the communities of the two experiments to characterizes sensor and to design and test the system architectures of ATLAS and CMS.

The full size pre-production chips were designed based on these results, having as a reference a common virtual baseline chip, called RD53B, which is adapted to the needs of each experiment (e.g. chip size, analog front-end, triggering features).

The RD53B-ATLAS version was submitted in March 2020 and it has been extensively tested, providing valuable results for the implementation of the RD53B-CMS version, which was submitted in June 2021 and is currently under test, with promising results.

RD53 Collaboration is now finalizing the design of the final chips, which will be sent to production in 2022.

In this presentation, a general overview of the chip architecture will be presented, as well as the first test results on the pre-production chips.

Relatore: Flavio Loddo

Data: 03/02/2022